Space and Time Co-Optimization in Electronic Design Automation

Abstract

In the conventional electronic design automation (EDA) flow, space and time decisions of logic operations are carried out in separate steps. In this talk, the speaker will show that co-optimization of space and time can be highly beneficial. In particular, he will present his team’s recent work on TAPA, which is a task-parallel dataflow high-level synthesis (HLS) framework that couples with physical planning. TAPA improves the final clock frequency by 2X and compiles 7X faster than Vitis HLS. TAPA framework won two Best Paper Awards at FPGA'21 and FPGA'22, and has been used successfully for developing efficient accelerators for a large number of applications, including stencil computation, graph processing, systolic arrays, and sparse linear algebra. If time permits, he will also discuss other EDA tools developed in his lab which applies space and time co-optimization successfully, including automated systolic array designs and quantum layout synthesis.

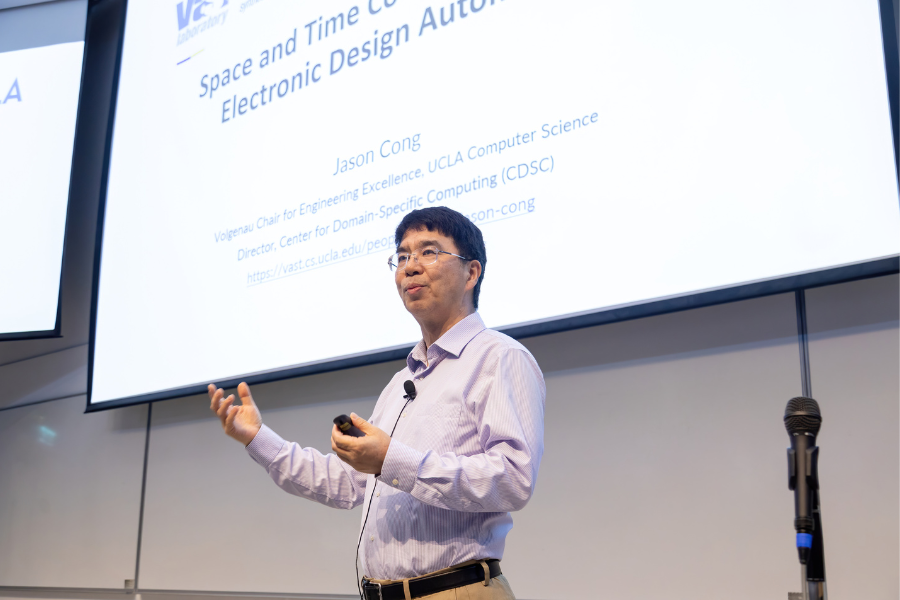

About the Speaker

Prof. Jason CONG is the Volgenau Chair for Engineering Excellence Professor at the UCLA Computer Science Department (and a former department chair), with joint appointment from the Electrical and Computer Engineering Department. He is the Director of Center for Domain-Specific Computing (CDSC) and the Director of VLSI Architecture, Synthesis, and Technology (VAST) Laboratory. His research interests include novel architectures and compilation for customizable computing, synthesis of VLSI circuits and systems, and quantum computing. He has over 500 publications in these areas, including 18 best paper awards, and 4 papers in the FPGA and Reconfigurable Computing Hall of Fame. He and his former students co-founded AutoESL, which developed the most widely used high-level synthesis tool for FPGAs (renamed to Vivado HLS and Vitis HLS after Xilinx’s acquisition). He is member of the National Academy of Engineering, and a Fellow of ACM, IEEE, and the National Academy of Inventors. He is recipient of the SIA University Research Award, the EDAA Achievement Award, and the IEEE Robert N. Noyce Medal for “fundamental contributions to electronic design automation and FPGA design methods”.

For Attendees' Attention

Seating is on a first come, first served basis.